#### LSD4RF-3V930SDA

#### WS7300-P915 BR 端 Pro 版标准模组

WS7300-P915 BR 端 Pro 版标准模组(以下简称 BR 子板)是基于利尔达自主研发的 WS7300 系列模组设计的,主要用于实现 Wi-SUN 千点组网功能,以满足客户大规模组网需求。

**前言** 本公司提供该文档内容用以支持其客户的产品设计。客户须按照文档中提供的规范,参数来设计其产品。由于客户操作不当而造成的人身伤害或财产损失,本公司不承担任何责任。在未声明前,本公司有权对该文档进行更新。

版权申明 本文档版权属于本公司,任何人未经我公司允许复制转载该文档将承担法律责任。

版权所有 © 利尔达科技集团,保留一切权利。

Copyright © Lierda Science & Technology Group Co.,Ltd

# 文件修订历史

| 版本    | 日期         | 变更描述                  |

|-------|------------|-----------------------|

| Rev01 | 2020-06-11 | 初始版本                  |

| Rev02 | 2020-07-21 | 完善规格参数、尺寸图、注意事项内容     |

| Rev03 | 2020-08-05 | 增加引脚功能说明表格、调整参考设计电路   |

| Rev04 | 2020-10-23 | 修改模块示意图、引脚功能说明表格及规格参数 |

| Rev05 | 2021-01-05 | 修改产品名称                |

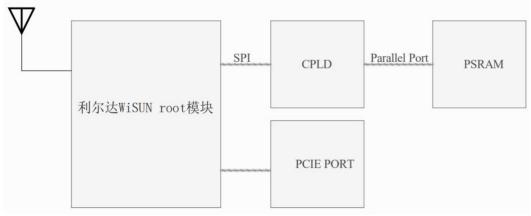

#### 1 硬件框图

图 1 是 BR 子板硬件功能框图,其中天线接口形式为 IPX 插座;Root 模组为利尔达自主设计的 Wi-SUN Root 模块 (硬件型号:LSD4RF-3V930SD0);PCIE PORT 适配标准 MINI PCI Express 52PIN 插座尺寸。

图 1 硬件框图

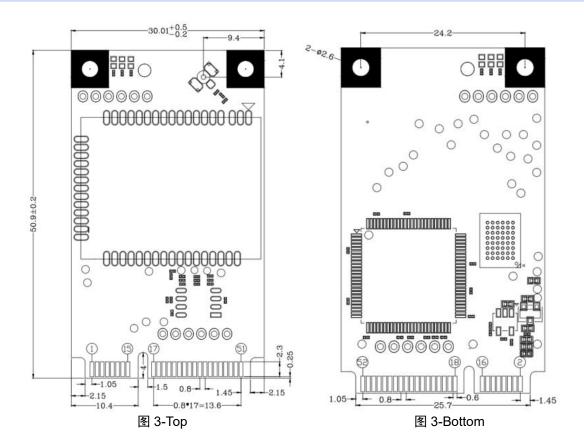

BR 子板外形示意图如图 2 所示。

图 2 BR 子板外形示意图

### 2 规格参数

表 1 极限参数

| 主要参数    | 性能   |     | 备注       |

|---------|------|-----|----------|

| 工安参数    | 最小值  | 最大值 | <b>一</b> |

| 电源电压(V) | -0.2 | 5.5 |          |

| 存储温度(℃) | -40  | 85  |          |

表 2 工作参数

|             |                   | W Z  | 11 2 35 |                      |

|-------------|-------------------|------|---------|----------------------|

| 主要参数        | 性能1               |      |         | A7 334-              |

| 土安勿知        | 最小值               | 典型值  | 最大值     | <b>备注</b>            |

| 工作电压 (V)    | 4                 | 5    | 5.25    | 推荐使用5V               |

| 工作频段(MHz)   | 902               | 915  | 928     | 客户可自定义工作频率           |

| 发射电流(mA)    | 600               | 750  | 850     | 发射功率28-30.5dBm       |

| 接收电流(mA)    | 32                | 39   | 80      | 最大值是CPLD和PSRAM运行时的状态 |

| 工作温度(℃)     | -40               |      | 85      |                      |

| 通信速率        |                   |      | 300kbps | 用户可编程自定义             |

| 天线接口        |                   | IPEX |         |                      |

| 调制方式        | OOK/GFSK/FSK/GMSK |      |         |                      |

| 接口类型        | MINI PCI Express  |      | oress   | 52PIN                |

| 通讯协议        | SPI/UART          |      |         |                      |

| 外形尺寸(mm)    | 50.95*30.2*4.6mm  |      | 6mm     | -                    |

| I/0口高电平(V)  | 2.4               | 3.3  | 3.6     |                      |

| I/0口低电平(V)  |                   |      | 0.8     |                      |

| PSRAM(Mbit) |                   | 64   |         |                      |

|             |                   |      |         |                      |

## 3 尺寸图及引脚定义

#### 3.1 尺寸图

BR 子板详细尺寸如图 3 所示,该模块使用标准 MINI PCIE 接口尺寸(这里仅采用了 MINI PCIE 接口物理尺寸及部分引脚定义,其他引脚定义根据需求有所调整),为双面器件焊接,Bottom和 Top 两面器件最大高度分别为 1.5mm和 3.0mm。注意:这里的尺寸图主要是为了说明板子形状与尺寸,PCB 板上的器件位置仅作示意(如后期 PCB 板上器件位置变动,此处不再做更新说明)。

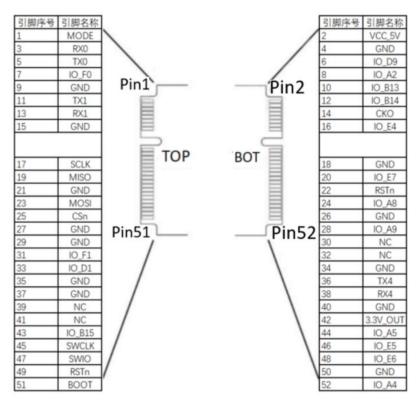

#### 3.2 引脚定义

BR 子板 MINI PCIE 接口引脚定义如图 4 所示。

图 4 引脚定义

表 3 引脚功能说明

| PIN        | 名称       | 描述                            |  |  |

|------------|----------|-------------------------------|--|--|

| 1          | MODE     | 模式选择,模块内部上拉 100kΩ,预留引脚,       |  |  |

|            |          | 内部悬空:                         |  |  |

|            |          | MODE=0: Debug mode            |  |  |

|            | 1100 511 | MODE=1: Normal mode           |  |  |

| 2          | VCC_5V   | 模块电源电压                        |  |  |

| 3          | RX0      | UARTO 接收引脚,模块内部 10KΩ上拉        |  |  |

| 5          | TX0      | UARTO 发送引脚                    |  |  |

| 11         | TX1      | UART1 发送引脚                    |  |  |

| 13         | RX1      | UART1 接收引脚,模块内部 10KΩ上拉        |  |  |

| 14         | СКО      | 内部时钟信号输出; 预留引脚, 内部悬空          |  |  |

| 17         | SCLK     | SPI 时钟信号;预留引脚,内部悬空            |  |  |

| 19         | MISO     | SPI 数据信号;预留引脚,内部悬空            |  |  |

| 22、49      | RSTn     | 模块复位信号,内部上拉 10kΩ,低电平复位有       |  |  |

|            |          | 效; PIN49 预留为 SWD 烧写接口复位,目前内   |  |  |

|            |          | 部为悬空,实际使用 PIN22 作为复位引脚        |  |  |

| 23         | MOSI     | SPI 数据信号;预留引脚,内部悬空            |  |  |

| 25         | CSn      | SPI 片选引脚; 预留引脚,内部悬空           |  |  |

| 30、32、39、  | NC       | 空引脚                           |  |  |

| 41         |          |                               |  |  |

| 36         | TX4      | UART4 发送引脚                    |  |  |

| 38         | RX4      | UART4 接收引脚                    |  |  |

| 42         | 3.3V_OUT | 模块 3.3V 输出,可用于小电流负载 Imax<50mA |  |  |

| 45         | SWCLK    | SWD 时钟信号, 预留引脚,内部悬空           |  |  |

| 47         | SWIO     | SWD 数据信号,预留引脚,内部悬空            |  |  |

| 51         | BOOT     | 启动方式选择,模块内部下拉 100kΩ;预留引       |  |  |

|            |          | 脚,内部悬空:                       |  |  |

|            |          | BOOT=0: 程序从 flash 启动          |  |  |

|            |          | BOOT=1: 程序从 iROM 启动           |  |  |

| 4、9、15、18、 |          |                               |  |  |

| 21、26、27、  |          |                               |  |  |

| 29、34、35、  | GND      | 系统地                           |  |  |

| 37、40、50   |          |                               |  |  |

| 其他         |          | 通用 I/O 引脚                     |  |  |

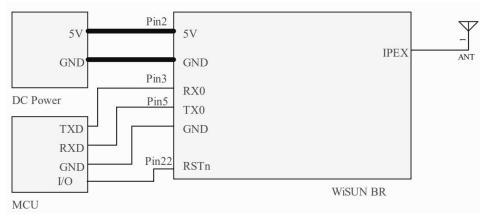

## 4 典型应用电路

使用 Wi-SUN BR 子板用作组网最基本的硬件电路请参考图 5 所示,图中 BR 子板上的 UARTO (TXO、RXO) 为应用通信串口,RSTn 为模块复位引脚可在代码运行异常时用于复位系统,模块复位引脚有效电平是低电平,模块 RSTn 引脚内部存在上拉电阻(10K  $\Omega$ )。

图 5 参考设计电路

## 5 注意事项

- 1) 模块天线输出接口阻抗为 50 Ω, 需要注意天线输入阻抗的匹配;

- 2) 模块安装在应用底板上后,如果需要在模块下方布局器件,需要注意模块Bottom面器件避让;

- 3) 模块在默认发射状态下电流消耗约为 750mA, 需要考虑到天线断开情况下阻抗失配时的电流可能会达到 1A, 注意模块供电电源的带载能力;

- 4) MODE、BOOT、RSTn 几个控制引脚模块内部已设置相应的上拉或下拉配置,如果连接至 MCU I/O,需要注意 I/O 状态配置;